Circuits Multi-Projets

MPW Services Center for IC / MEMS Prototyping

http://cmp.imag.fr

**Grenoble - France**

# Context & Motivation

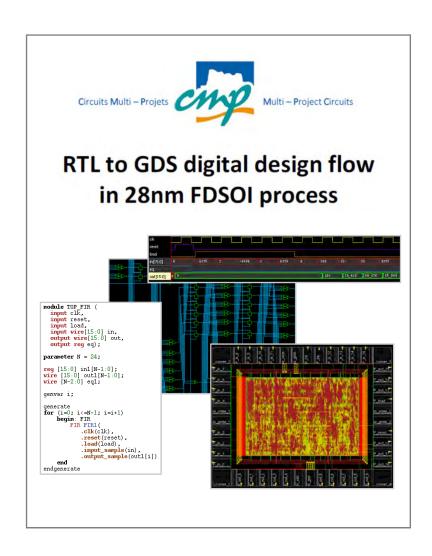

- ✓ A basic version of this tutorial was developed in 2015 (v1.4).

- ✓ A second version with several updates and additional functionalities was released on summer 2016 (v2.3).

- ✓ Introduce the digital design thanks to a plug and play tutorial:

- ✓ each step from RTL to GDSII is detailed,

- ✓ based on standard methodologies and CAD tools,

- ✓ all scripts and testbenches are provided,

- ✓ illustrated from a **simple digital circuit** example,

- implemented on an advanced technology,

- ✓ integrates body biasing functionalities.

#### Verilog RTL

```

always @ (negedge clk)

begin

if (load == 1)

eq <= 0;

if (eq1 == 0)

else

eq <= 1;

```

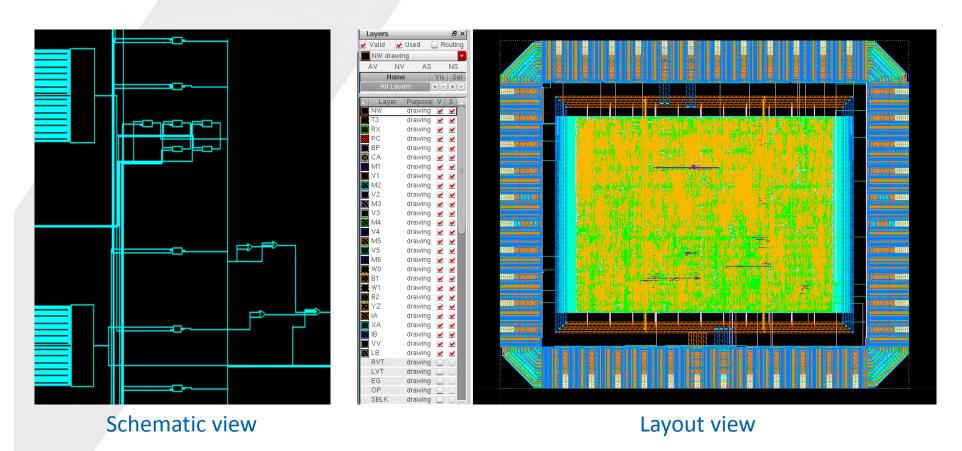

**GDSII** layout

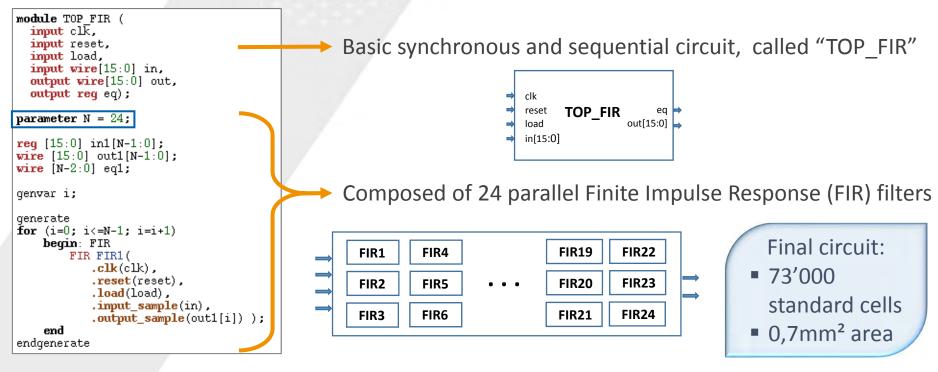

# RTL to GDS flow: FIR circuit example

## RTL to GDS flow: logic synthesis

#### Verilog RTL

### Synthesis tool

Design Compiler (Synopsys)

Genus (Cadence)

Genus: Next generation of RTL Compiler

#### Gate level netlist

## RTL to GDS flow: place and route

#### Gate level netlist

+ top cell "PAD\_TOP\_FIR" (including IOs)

```

module PAD TOP FIR ( clk, reset, load, in, out, eq );

imput [1\overline{5}:0] in;

output [15:0] out;

input clk, reset, load;

output eq;

wire w_clk, w_reset, w_load, w_eq;

wire [15:0] w_out, w_in;

wire [16:0] node float;

wire netTiel, netTie0;

TOP_FIR I_TOP_FIR (.clk(w_clk), .reset(w_reset), .load

```

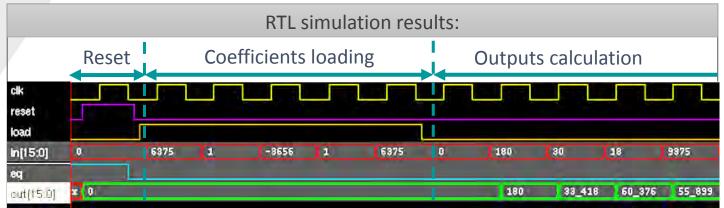

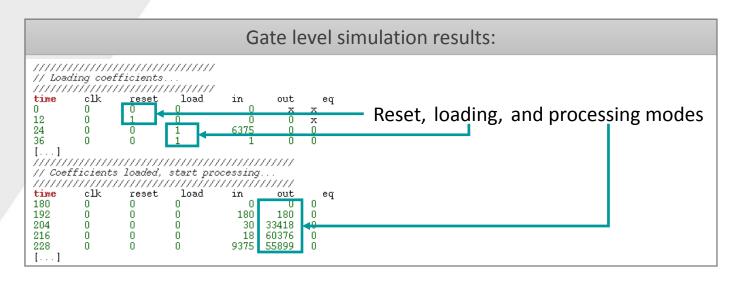

#### Back-annotated simulation results:

```

Annotating SDF timing data:

Compiled SDF file:

PAD TOP FIR routed genus.sdf.X

Log file:

sdffile rc. log

Backannotation scope: top. U

Configuration file:

Annotation completed successfully...

// Loading coefficients...

reset load

n

0

12

24

36

// Coefficients loaded, start processing.

reset load

out

180

192

180

204

30 33418

216

18 60376

228

9375 55899

[...]

```

Tech, files issued from ST's new FoundationTechnoKits

Place & route tool

Innovus (Cadence)

Place & route script updated for Innovus 15.20.000

### Verilog netlist

```

module PAD_TOP_FIR (

reset,

load,

in,

out,

eq);

imput clk;

imput reset;

imput load;

input [15:0] in;

output [15:0] out;

output eq;

```

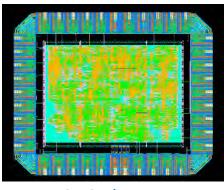

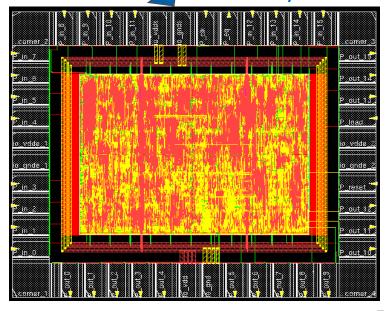

**GDSII** layout

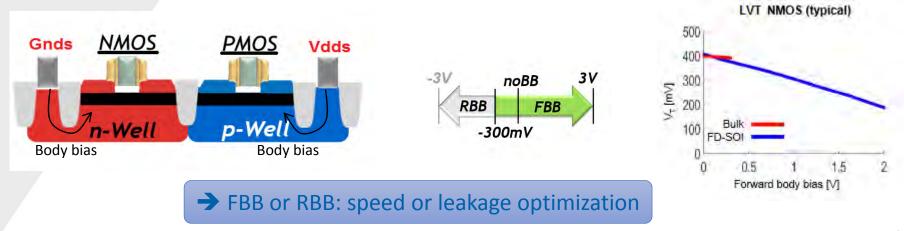

## 28nm FDSOI features during place and route

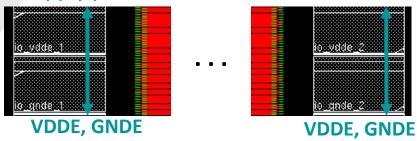

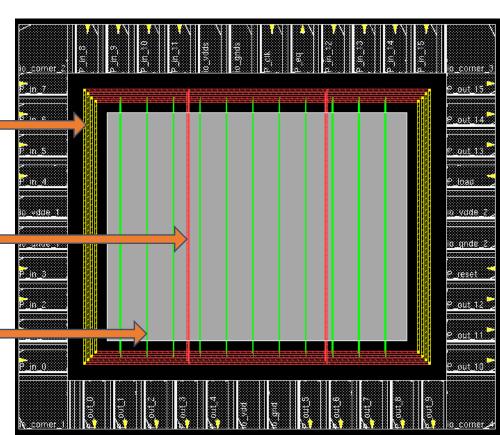

## **IOs placement:**

✓ Addition of 2 specific pads dedicated to supply VDDS and GNDS body biasing

voltages (-1,8V to +1,8V):

✓ Addition of an IO filler cell to tie high or low the compensation signals:

✓ 2 supply pairs VDDE and GNDE:

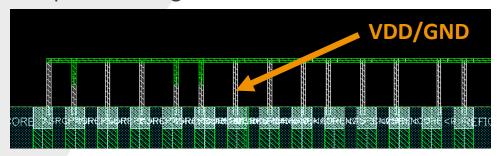

## Floorplan and power plan generation:

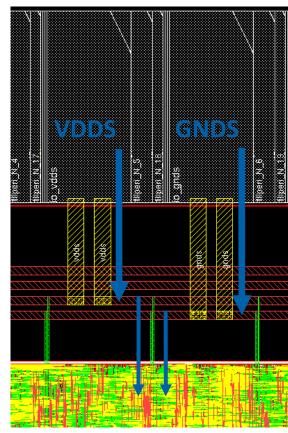

- ✓ 4 power rings (VDD, GND, VDDS, GNDS) drawn with thickest metal layers.

- ✓ 2 pairs of power stripes to feed the circuit with VDD and GND

- ✓ 1 pair of VDDS/GNDS stripes every 50µm spacing to feed body biasing voltages to standard cells

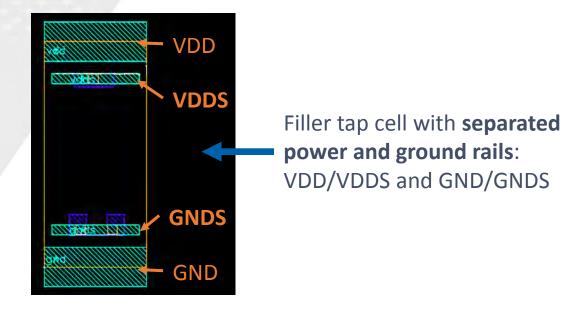

## 28nm FDSOI features during place and route

### Core cells placement and routing:

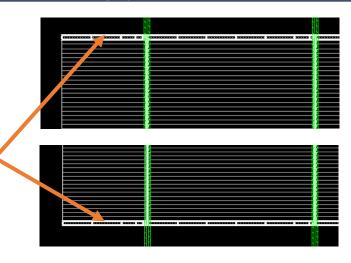

✓ Fillers cells on top and bottom core rows (to meet particular DRC rules)

✓ Implementation of filler tap cells with separated power and ground rails (dedicated connections to bodies of standard cells)

✓ Restriction of the tool to use the 8 first metal layers to route signals, and the 2 top layers for power.

# Final verifications

✓ GDSII and netlist can be imported under Cadence Virtuoso 6.1.6:

✓ LVS and DRC verifications can be performed

# Tutorial delivery

- ✓ 118 institutions received in 2016 this upgraded version of the tutorial

- ✓ Developed in CMOS28FDSOI technology, with PDK version 2.5.f

- ✓ can be easily adapted for PDK 2.7.a

- ✓ A third tutorial release is planned Q2 2017 for latest CMOS28FDSOI PDK 2.9

- migration from 10ML to 8 metal layers stack,

- ✓ LVS and DRC verifications.

- ✓ Still positive feedback from designers!

# Thank you!

## Body biasing methodology flow

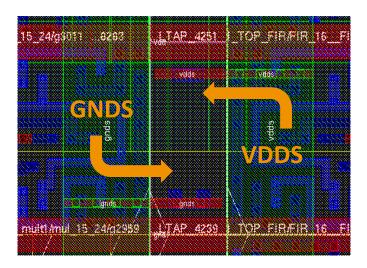

### Body biasing in layout view:

#### Body biasing on LVT (flip-well) transistors: